Products

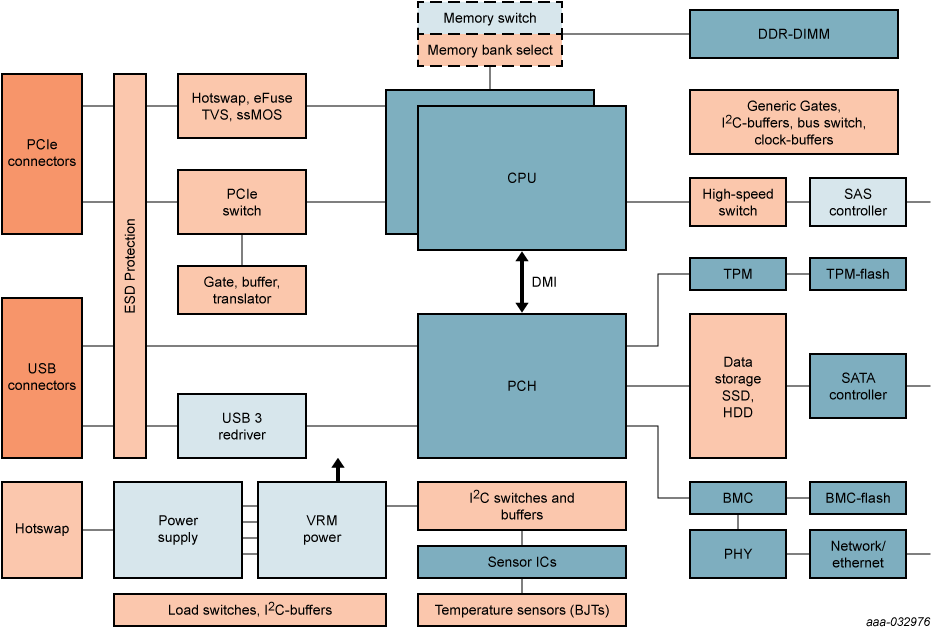

Design considerations

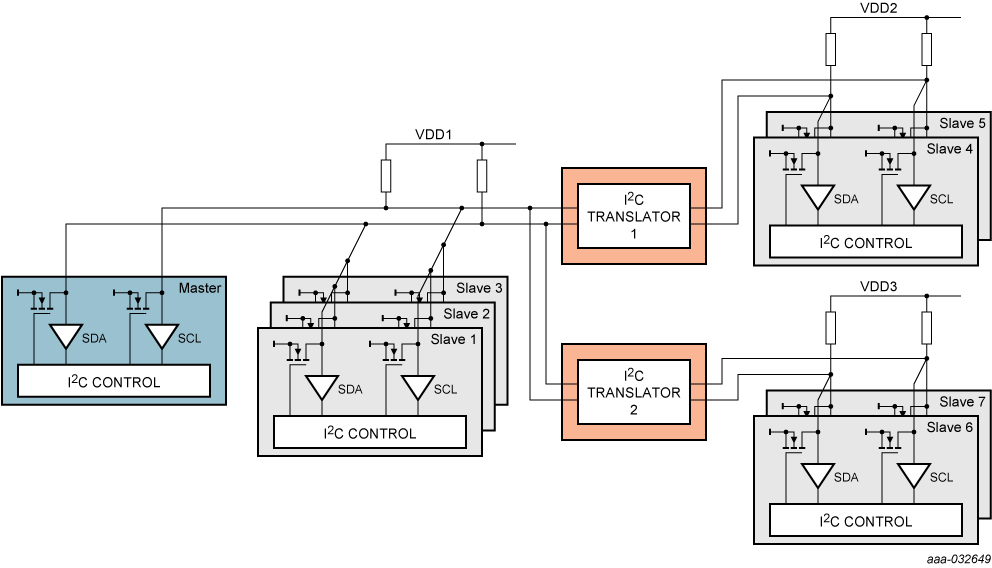

- Multi-voltage bus branches are common and need support of clock-stretching and partial power down is a requirement

- Signals require higher drive capability, logic function required for control signals

- Main boards and PCIe boards need to be exchanged without system power-down - in-rush currents must limited

- Sensitive SoC inputs and outputs require ESD protection while maintaining high data rates and signal integrity (Ethernet, PCIe, SATA, USB3, USB4 and Thunderbolt 3)

I2C voltage translation and repeaters

For I2C master/slave interfaces there is a trend towards higher bus speed, with multi-voltage bus branches common and a need for support of clock-stretching. Regardless of the complexity, Nexperia can offer a solution to meet your needs.

Logic Application Handbook

Download Nexperia’s Logic Design Engineer’s Guide and get a better understanding of Logic products, their features and properties, timing and interfacing aspects as well as get an overview of application insights.